hal_ucs.h File Reference

Universal clock system configuration. More...

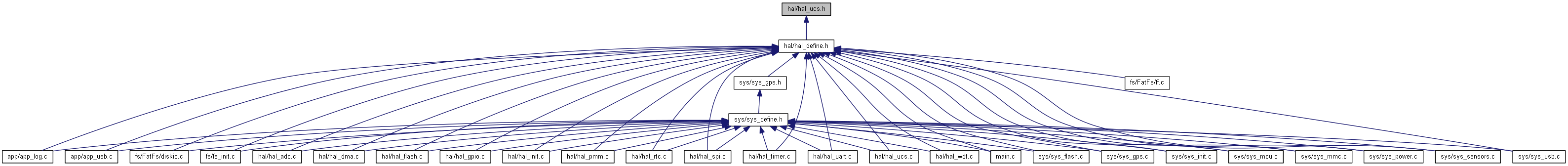

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | HAL_UCS_Init () |

| Initializing universal clock system. | |

Detailed Description

Universal clock system configuration.

Definition in file hal_ucs.h.

Function Documentation

| void HAL_UCS_Init | ( | ) |

Initializing universal clock system.

- Returns

- void

- Parameters

-

void

Definition at line 21 of file hal_ucs.c.

{

unsigned int uiXT1Timeout = 50000;

unsigned int uiXT2Timeout = 50000;

while (BAKCTL & LOCKBAK) BAKCTL &= ~LOCKBAK;

// XT1 (32768Hz)

UCSCTL6 |= XT1DRIVE1 + XT1DRIVE0;

UCSCTL6 &= ~XT1OFF; // Set XT1 On

UCSCTL6 &= ~(XCAP1 + XCAP0); // Internal load cap

__delay_cycles(50000); // Delay until XT2 is stabilized

do // Loop until XT1 stabilizes

{

UCSCTL7 &= ~XT1LFOFFG; // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while ((UCSCTL7 & XT1LFOFFG) && --uiXT1Timeout); // Check XT2 fault flag

// XT2 (12000000Hz)

UCSCTL6 |= XT2DRIVE0; // Drive strength set to range of 8MHz to 16MHz

UCSCTL6 &= ~XT2OFF; // Set XT2 On

__delay_cycles(50000); // Delay until XT2 is stabilized

do // Loop until XT2 stabilizes

{

UCSCTL7 &= ~XT2OFFG; // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while ((UCSCTL7 & XT2OFFG) && --uiXT2Timeout); // Check XT2 fault flag

// Clock selection

UCSCTL4 |= SELA_0 + SELS_5 + SELM_5; // Select SMCLK, ACLK source and DCO source

}

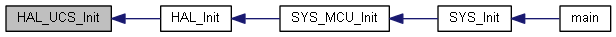

Here is the caller graph for this function: