PMM configuration. More...

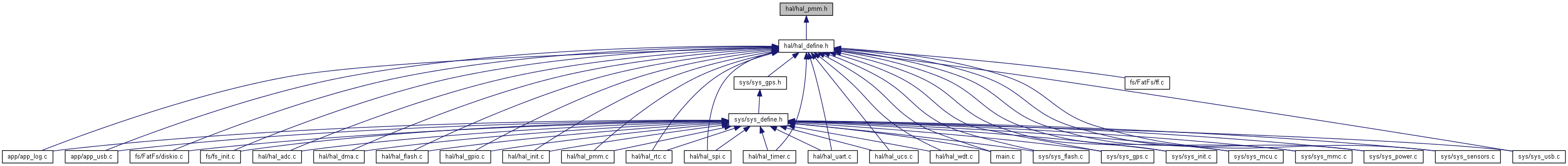

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | HAL_ENTER_LPM4() __bis_SR_register(LPM4_bits + GIE) |

| #define | ENABLE_SVSL() st(PMMCTL0_H = 0xA5; SVSMLCTL |= SVSLE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSL() st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~SVSLE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVML() st(PMMCTL0_H = 0xA5; SVSMLCTL |= SVMLE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVML() st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~SVMLE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVSH() st(PMMCTL0_H = 0xA5; SVSMHCTL |= SVSHE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSH() st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~SVSHE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVMH() st(PMMCTL0_H = 0xA5; SVSMHCTL |= SVMHE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVMH() st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~SVMHE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVSL_SVML() st(PMMCTL0_H = 0xA5; SVSMLCTL |= (SVSLE + SVMLE); PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSL_SVML() st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~(SVSLE + SVMLE); PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVSH_SVMH() st(PMMCTL0_H = 0xA5; SVSMHCTL |= (SVSHE + SVMHE); PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSH_SVMH() st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~(SVSHE + SVMHE); PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVSL_RESET() st(PMMCTL0_H = 0xA5; PMMRIE |= SVSLPE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSL_RESET() st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVSLPE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVML_INTERRUPT() st(PMMCTL0_H = 0xA5; PMMRIE |= SVMLIE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVML_INTERRUPT() st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVMLIE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVSH_RESET() st(PMMCTL0_H = 0xA5; PMMRIE |= SVSHPE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVSH_RESET() st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVSHPE; PMMCTL0_H = 0x00; ) |

| #define | ENABLE_SVMH_INTERRUPT() st(PMMCTL0_H = 0xA5; PMMRIE |= SVMHIE; PMMCTL0_H = 0x00; ) |

| #define | DISABLE_SVMH_INTERRUPT() st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVMHIE; PMMCTL0_H = 0x00; ) |

| #define | CLEAR_PMM_IFGS() st(PMMCTL0_H = 0xA5; PMMIFG = 0; PMMCTL0_H = 0x00; ) |

| #define | SVSL_ENABLED_IN_LPM_FAST_WAKE() |

| #define | SVSL_ENABLED_IN_LPM_SLOW_WAKE() |

| #define | SVSL_DISABLED_IN_LPM_FAST_WAKE() |

| #define | SVSL_DISABLED_IN_LPM_SLOW_WAKE() |

| #define | SVSH_ENABLED_IN_LPM_NORM_PERF() |

| #define | SVSH_ENABLED_IN_LPM_FULL_PERF() |

| #define | SVSH_DISABLED_IN_LPM_NORM_PERF() |

| #define | SVSH_DISABLED_IN_LPM_FULL_PERF() |

| #define | SVSL_OPTIMIZED_IN_LPM_FAST_WAKE() |

| #define | SVSH_OPTIMIZED_IN_LPM_FULL_PERF() |

| #define | PMM_STATUS_OK 0 |

| #define | PMM_STATUS_ERROR 1 |

Functions | |

| void | HAL_PMM_Init (void) |

| Initializing PMM. | |

| uint16_t | SetVCore (uint8_t level) |

Detailed Description

PMM configuration.

Definition in file hal_pmm.h.

Macro Definition Documentation

| #define CLEAR_PMM_IFGS | ( | ) | st(PMMCTL0_H = 0xA5; PMMIFG = 0; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVMH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~SVMHE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVMH_INTERRUPT | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVMHIE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVML | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~SVMLE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVML_INTERRUPT | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVMLIE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~SVSHE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSH_RESET | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVSHPE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSH_SVMH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL &= ~(SVSHE + SVMHE); PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSL | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~SVSLE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSL_RESET | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE &= ~SVSLPE; PMMCTL0_H = 0x00; ) |

| #define DISABLE_SVSL_SVML | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL &= ~(SVSLE + SVMLE); PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVMH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL |= SVMHE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVMH_INTERRUPT | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE |= SVMHIE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVML | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL |= SVMLE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVML_INTERRUPT | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE |= SVMLIE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL |= SVSHE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSH_RESET | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE |= SVSHPE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSH_SVMH | ( | ) | st(PMMCTL0_H = 0xA5; SVSMHCTL |= (SVSHE + SVMHE); PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSL | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL |= SVSLE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSL_RESET | ( | ) | st(PMMCTL0_H = 0xA5; PMMRIE |= SVSLPE; PMMCTL0_H = 0x00; ) |

| #define ENABLE_SVSL_SVML | ( | ) | st(PMMCTL0_H = 0xA5; SVSMLCTL |= (SVSLE + SVMLE); PMMCTL0_H = 0x00; ) |

| #define HAL_ENTER_LPM4 | ( | ) | __bis_SR_register(LPM4_bits + GIE) |

| #define SVSH_DISABLED_IN_LPM_FULL_PERF | ( | ) |

| #define SVSH_DISABLED_IN_LPM_NORM_PERF | ( | ) |

| #define SVSH_ENABLED_IN_LPM_FULL_PERF | ( | ) |

| #define SVSH_ENABLED_IN_LPM_NORM_PERF | ( | ) |

| #define SVSH_OPTIMIZED_IN_LPM_FULL_PERF | ( | ) |

| #define SVSL_DISABLED_IN_LPM_FAST_WAKE | ( | ) |

| #define SVSL_DISABLED_IN_LPM_SLOW_WAKE | ( | ) |

| #define SVSL_ENABLED_IN_LPM_FAST_WAKE | ( | ) |

| #define SVSL_ENABLED_IN_LPM_SLOW_WAKE | ( | ) |

| #define SVSL_OPTIMIZED_IN_LPM_FAST_WAKE | ( | ) |

Function Documentation

| void HAL_PMM_Init | ( | void | ) |

Initializing PMM.

- Returns

- void

- Parameters

-

void

Definition at line 24 of file hal_pmm.c.

{

SysRstIv = SYSRSTIV;

// Set Vcore voltage to level 2 in order to support 12MHz MCLK

// SVSH enabled

// SVSHRVL = 2 (2.04V), SVSMHRRL = 2 (2.14V)

SetVCore(2);

// Enable SYSH and SVMH

// Enable SVSH reset

// SVS is enabled in LPM as normal performance

// Clear existing interrupt flags

}

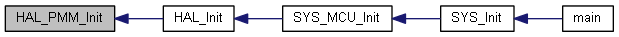

Here is the call graph for this function:

Here is the caller graph for this function:

| uint16_t SetVCore | ( | uint8_t | level | ) |

Definition at line 272 of file hal_pmm.c.

{

uint16_t actlevel;

uint16_t status = 0;

level &= PMMCOREV_3; // Set Mask for Max. level

actlevel = (PMMCTL0 & PMMCOREV_3); // Get actual VCore

// step by step increase or decrease

while ((level != actlevel) && (status == 0)) {

if (level > actlevel){

status = SetVCoreUp(++actlevel);

}

else {

status = SetVCoreDown(--actlevel);

}

}

return status;

}

Here is the caller graph for this function: